Approved Product

#### **PRODUCT FEATURES**

- Supports Power PC CPU's.

- Supports simultaneous PCI and Fast PCI Buses.

- Uses external buffer to reduce EMI and Jitter

- PCI synchronous clock.

- Fast PCI synchronous clock

- Separated 3.3 volt power supplies for reduced Jitter

- < 500 pS skew between CPU and PCI clocks</p>

- Programmable features:

- frequency selection

- margin testing frequency increases

- Output Enable for board level testing

- CPU to PCI clock offset selection

- Independent VDD supplies for all output clocks

- 28-pin SSOP 209 mil. package

- Spread Spectrum Technology for EMI reduction

- Internal Crystal Load Capacitors for 20 pF parallel resonant crystal support.

#### FREQUENCY TABLE (MHz)

|     |     |     |              | . ,    |        |

|-----|-----|-----|--------------|--------|--------|

| FS2 | FS1 | FS0 | CPU          | PCI    | PCIF   |

| 0   | 0   | 0   | 90           | 30.0   | 60.0   |

| 0   | 0   | 1   | 94.5(90+5%)  | 31.5   | 63     |

| 0   | 1   | 0   | 66.6*        | 33.3*  | 66.6*  |

| 0   | 1   | 1   | 70(66+5%)**  | 35**   | 70**   |

| 1   | 0   | 0   | 100.0(99.6)* | 33.3*  | 66.6*  |

| 1   | 0   | 1   | 105.0**      | 35.0** | 69.9** |

| 1   | 1   | 0   | 120.0(119.9) | 30.0   | 60.0   |

| 1   | 1   | 1   | 133.0**      | 33.3** | 66.6** |

\* indicates 0.5 % down spread spectrum capable

\*\* See TEST MODE table for functional definition when SSON is low

#### TEST MODE. FUNCTIONALITY NOT GUARANTEED OVER FULL TEMPERATURE AND VOLTAGE

Rev.2.1

**Approved Product**

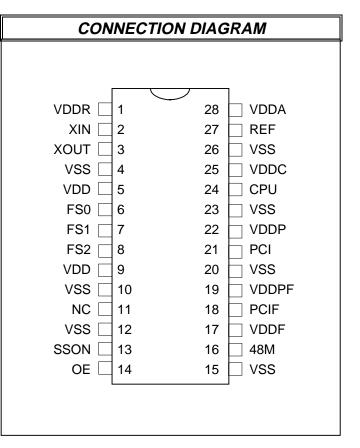

| PIN DESCRIPTION              |          |           |         |                                                                                                                                                                                                                                                                                              |  |  |  |  |

|------------------------------|----------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Number                   | Pin Name | PWR       | I/O     | Description                                                                                                                                                                                                                                                                                  |  |  |  |  |

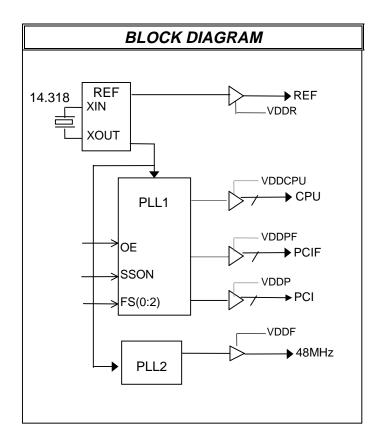

| 2                            | XIN      | VDD       | I       | These pins form an on-chip reference oscillator when<br>connected to terminals of an external parallel resonant<br>crystal (nominally 14.318 MHz). Xin may also serve as<br>input for an externally generated reference signal. If the<br>external input is used, Pin 3 is left unconnected. |  |  |  |  |

| 3                            | XOUT     | VDD       | 0       |                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 18                           | PCIF     | VDDP      | 0       | 66.6 Mhz FAST PCI clock rising edge synchronized to the CPU clock.                                                                                                                                                                                                                           |  |  |  |  |

| 21                           | PCI      | VDDP      | 0       | 33.3 Mhz PCI clock rising edge synchronized to the CPU clock.                                                                                                                                                                                                                                |  |  |  |  |

| 17                           | VDDF     | -         | PWR     | Power for 48 Mhz fixed clock buffer.                                                                                                                                                                                                                                                         |  |  |  |  |

| 19                           | VDDPF    | -         | PWR     | Power for FAST PCI (66 Mhz) clock buffer and PCIF (66 Mhz) clock buffer                                                                                                                                                                                                                      |  |  |  |  |

| 22                           | VDDP     | -         | PWR     | Power for PCI (33 Mhz) clock buffer and PCIF (66 Mhz) clock buffer                                                                                                                                                                                                                           |  |  |  |  |

| 24                           | CPU      | VDDC      | 0       | CPU clock output. See table on page 1 for frequencies.                                                                                                                                                                                                                                       |  |  |  |  |

| 13                           | SSON     | VDD       | I<br>PU | Spread Spectrum clock modulation pin. Enables Spread<br>Spectrum EMI reduction when at a logic low (0) level. Has<br>an internal pull-up resistor.                                                                                                                                           |  |  |  |  |

| 16                           | 48M      | VDDF      | 0       | This pin is a fixed frequency 48 Mhz clock output.                                                                                                                                                                                                                                           |  |  |  |  |

| 14                           | OE       | VDD       | Ι       | Output enable. When at logic level low causes all clock outputs to be in a Tri-state mode. Has internal pull-up resistor.                                                                                                                                                                    |  |  |  |  |

| 27                           | REF      | VDD       | 0       | This pin is a Buffered output copy of the crystal reference frequency.                                                                                                                                                                                                                       |  |  |  |  |

| 6, 7, 8                      | FS[0:2]  | VDD<br>PU | I       | Frequency selection input pins. See table on page 1 for functionality. Contain internal pull-up resistors.                                                                                                                                                                                   |  |  |  |  |

| 4, 10, 12, 15, 20,<br>23, 26 | VSS      | -         | PWR     | Ground pins for the chip.                                                                                                                                                                                                                                                                    |  |  |  |  |

| 5, 9, 28                     | VDD      | -         | PWR     | Power supply pins for analog circuit and core logic.                                                                                                                                                                                                                                         |  |  |  |  |

| 25                           | VDDC     | -         | PWR     | Power supply for CPU clock output buffer.                                                                                                                                                                                                                                                    |  |  |  |  |

| 1                            | VDDR     | -         | PWR     | Power supply for reference clock output buffer.                                                                                                                                                                                                                                              |  |  |  |  |

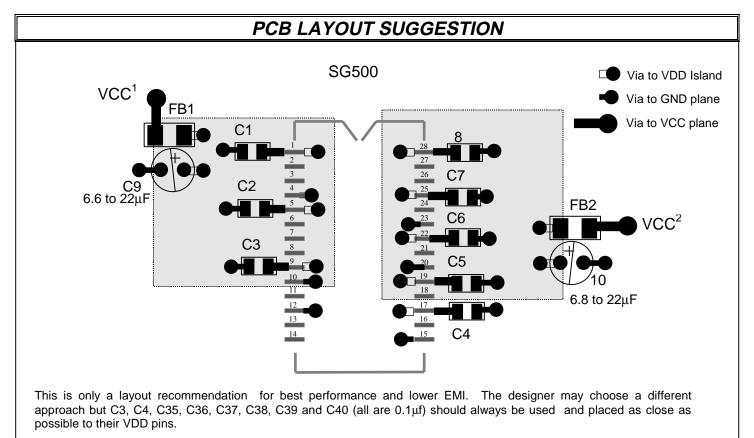

A bypass capacitor (0.1 $\mu$ F) should be placed as close as possible to each Vdd pin. If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be canceled by the lead inductance's of the traces.

### Low Jitter Spectrum Clock Generator for PowerPC Designs. Approved Product

### SPREAD SPECTRUM CLOCK GENERATION (SSCG)

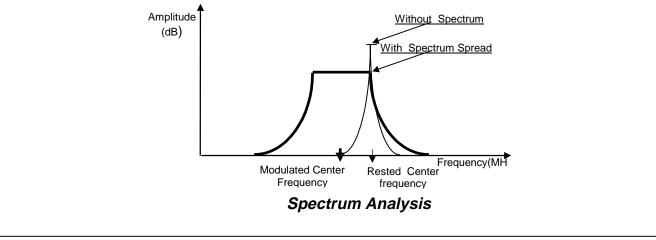

Spread Spectrum is a modulation technique applied here for maximum efficiency in minimizing Electro-Magnetic Interference radiation generated from repetitive digital signals mainly clocks. A clock accumulates EM energy at the center frequency it is generating. Spread Spectrum distributes this energy over a small frequency bandwidth therefore spreading the same amount of energy over a spectrum. This technique is achieved by modulating the clock down from its resting frequency by a certain percentage (which also determines the energy distribution bandwidth). In this product, the modulation is 1.0% down from the resting frequency.

### TEST MODE CONTROL TABLE

The FS0, 1 and 2 pin table on page 1 defines the function of these pins in setting the output clock frequencies. When the SSO# pin is brought to a logic low state the function of this table is modified. The following table indicates the effect of this signal when the SSON# pin is at low logic level

| SSON | FS2 | FS1 | FS0 | CPU      | PCI      | PCIF     | 48M      | REF      |

|------|-----|-----|-----|----------|----------|----------|----------|----------|

| 0    | 0   | 0   | 0   | 90.0     | 30.0     | 60.0     | 48       | 14.318   |

| 0    | 0   | 0   | 1   | 94.5     | 31.5     | 63       | 48       | 14.318   |

| 0    | 0   | 1   | 0   | 66.6     | 33.3     | 66.6     | 48       | 14.318   |

| 0    | 0   | 1   | 1   | TriState | TriState | TriState | TriState | TriState |

| 0    | 1   | 0   | 0   | 100 SS   | 33.3 SS  | 66.6 SS  | 48       | 14.318   |

| 0    | 1   | 0   | 1   | T2*      | T2*      | T2*      | T2*      | T2*      |

| 0    | 1   | 1   | 0   | 120      | 30       | 60       | 48       | 14.318   |

| 0    | 1   | 1   | 1   | XIN/2    | XIN/4    | XIN/2    | XIN      | XIN      |

Note: (All frequencies are in Mhz, Xin defines the clock applied to the XIN pin for testing purposes, and SS = Spread Spectrum.) T2 is a IMI device test mode and is not intended for customer use.

Approved Product

MAXIMUM RATINGS

| Voltage Relative to VSS: | -0.3V            |

|--------------------------|------------------|

| Voltage Relative to VDD: | 0.3V             |

| Storage Temperature:     | -65°C to + 150°C |

| Operating Temperature:   | 0 °C to +70 °C   |

| Maximum Power Supply:    | 7V               |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range: VSS<(Vin or Vout)<VDD Unused inputs must always be tied to an appropriate logic voltage level (either VSS or VDD).

| ELECTRICAL CHARACTERISTICS |        |     |     |     |       |                                 |  |  |

|----------------------------|--------|-----|-----|-----|-------|---------------------------------|--|--|

| Characteristic             | Symbol | Min | Тур | Мах | Units | Conditions                      |  |  |

| Input Low Voltage          | VIL    | -   | -   | 1.0 | Vdc   | -                               |  |  |

| Input High Voltage         | VIH    | 2.3 | -   | -   | Vdc   | -                               |  |  |

| Input Low Current          | IIL    |     |     | -66 | μA    |                                 |  |  |

| Input High Current         | IIH    |     |     | 5   | μA    |                                 |  |  |

| Tri-State leakage Current  | loz    | -   | -   | 10  | μA    |                                 |  |  |

| Dynamic Supply Current     | Idd    | -   | -   | 100 | mA    | CPU = 100 MHz                   |  |  |

| Static Supply Current      | Isdd   | -   | -   | 6   | mA    | OE = 0 (logic low)              |  |  |

| Short Circuit Current      | ISC    | 25  | -   | -   | mA    | 1 output at a time - 30 seconds |  |  |

*VDD* = *VDDC* = *VDDP* = *VDDF* = *VDDF* = *VDDR* =3.15 - 3.45*V* , *TA* = 0°*C* to +70°*C*

| SWITCHING CHARACTERISTICS                                            |        |     |     |              |       |                             |  |  |

|----------------------------------------------------------------------|--------|-----|-----|--------------|-------|-----------------------------|--|--|

| Characteristic                                                       | Symbol | Min | Тур | Мах          | Units | Conditions                  |  |  |

| Output Duty Cycle                                                    | -      | 45  | 50  | 55           | %     | Measured at 1.5V            |  |  |

| Skew (CPU to CPU)                                                    | tSKEW1 | -   | -   | ±250         | pS    | 30 pF Load Measured at 1.5V |  |  |

| Skew (CPU to PCI or PCIF)                                            | tSKEW1 | -   | -   | ±375         | pS    | 30 pF Load Measured at 1.5V |  |  |

| Skew (PCI or PCIF<br>to PCI)                                         | tSKEW2 | -   | -   | ±250         | pS    | 30 pF Load Measured at 1.5V |  |  |

| ∆Period Adjacent<br>Cycles                                           | ΔPA    | -   | -   | <u>+</u> 250 | pS    | -                           |  |  |

| Jitter Spectrum<br>Long term                                         | ΔPL    |     |     | <u>+</u> 500 | pS    | Measured over 10 Seconds    |  |  |

| VDD = VDDC= VDDP = VDDF = VDDF = VDDR =3.15-3.45V, TA = 0°C to +70°C |        |     |     |              |       |                             |  |  |

#### Low Jitter Spectrum Clock Generator for PowerPC Designs. Approved Product

| TB41 BUFFER CHARACTERISTICS FOR CPU, PCI, PCIF, REF and 48M                                                 |                    |     |     |     |       |                   |  |  |

|-------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-----|-------|-------------------|--|--|

| Characteristic                                                                                              | Symbol             | Min | Тур | Max | Units | Conditions        |  |  |

| Pull-Up Current Min                                                                                         | IOH <sub>min</sub> | 30  | -   | 39  | mA    | Vout = Vdd - 0.5V |  |  |

| Pull-Up Current Max                                                                                         | IOH <sub>max</sub> | 75  | -   | 109 | mA    | Vout = 1.5V       |  |  |

| Pull-Down Current Min                                                                                       | IOL <sub>min</sub> | 30  | -   | 40  | mA    | Vout = 0.4V       |  |  |

| Pull-Down Current Max                                                                                       | IOL <sub>max</sub> | 75  | -   | 103 | mA    | Vout = 1.2V       |  |  |

| Rise/Fall Time Min<br>Between 0.4 V and 2.4 V                                                               | TRF <sub>min</sub> | 0.5 | -   | -   | nS    | 15 pF Load        |  |  |

| Rise/Fall Time Max TRF <sub>max</sub> - - 2.0 nS 30 pF Load   Between 0.4 V and 2.4 V - - 2.0 nS 30 pF Load |                    |     |     |     |       |                   |  |  |

| VDD = VDDP = VDDF = VDDF = VDDR =3.15 - 3.45 V , TA = 0°C to +70°C                                          |                    |     |     |     |       |                   |  |  |

CRYSTAL AND REFERENCE OSCILLATOR PARAMETERS Characteristic Symbol Min Max Units Conditions Typ 12.00 Frequency  $F_{o}$ 14.31818 16.00 MHz ΤС +/-100 PPM Calibration note 1 Tolerance --ΤS +/- 100 PPM Stability (Ta -10 to +60C) note 1 --ΤA PPM --5 Aging (first year @ 25C) note 1 Parallel Resonant Mode OM --**Pin Capacitance** CP 36 pF Capacitance of XIN and Xout pins to ground (each) V DC Bias Voltage VBIAS 0.3Vdd Vdd/2 0.7Vdd Startup time Ts -30 μS CL Load Capacitance 20 pF The crystals rated load. note 1 --Effective Series -R1 -40 Ohms resistance (ESR) **Power Dissipation** DL mW note 1 0.10 -crystals internal package CO 8 pF Shunt Capacitance -capacitance (total)

For maximum accuracy, the total circuit loading capacitance should be equal to CL. This loading capacitance is the effective capacitance across the crystal pins and includes the device pin capacitance (CP) in parallel with any circuit traces, the clock generator and any onboard discrete load capacitors. Budgeting Calculations Typical trace capacitance, (< half inch) is 4 pF, Load to the crystal is therefore = 2.0 pF Clock generator internal pin capacitance of 36 pF, Load to the crystal is therefore = 18.0 pF

the total parasitic capacitance would therefore be

Note 1: It is recommended but not mandatory that a crystal meets these specifications.

INTERNATIONAL MICROCIRCUITS, INC. 525 LOS COCHES ST. MILPITAS, CA 95035. TEL: 408-263-6300. FAX 408-263-6571 Rev.2.1

= 20.0 pF.

Approved Product

**Approved Product**

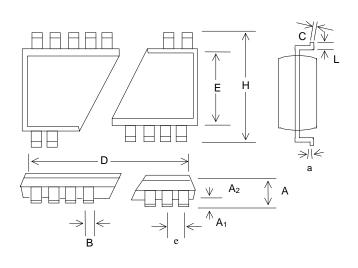

#### PACKAGE DRAWING AND DIMENSIONS

| 28 PIN SSOP OUTLINE DIMENSIONS |        |           |       |             |         |       |  |  |

|--------------------------------|--------|-----------|-------|-------------|---------|-------|--|--|

|                                |        | INCHES    |       | MILLIMETERS |         |       |  |  |

| SYMBOL                         | MIN    | NOM       | MAX   | MIN         | NOM     | MAX   |  |  |

| А                              | 0.068  | 0.073     | 0.078 | 1.73        | 1.86    | 1.99  |  |  |

| A <sub>1</sub>                 | 0.002  | 0.005     | 0.008 | 0.05        | 0.13    | 0.21  |  |  |

| A2                             | 0.066  | 0.068     | 0.070 | 1.68        | 1.73    | 1.78  |  |  |

| В                              | 0.010  | 0.012     | 0.015 | 0.25        | 0.30    | 0.38  |  |  |

| С                              | 0.005  | 0.006     | 0.009 | 0.13        | 0.15    | 0.22  |  |  |

| D                              | 0.397  | 0.402     | 0.407 | 10.07       | 10.20   | 10.33 |  |  |

| E                              | 0.205  | 0.209     | 0.212 | 5.20        | 5.30    | 5.38  |  |  |

| е                              | 0.     | .0256 BSC | )     |             | 0.65 BS | С     |  |  |

| н                              | 0.301` | 0.307     | 0.311 | 7.65        | 7.80    | 7.90  |  |  |

| а                              | 0°     | 4°        | 8°    | 0°          | 4°      | 8°    |  |  |

| L                              | 0.022  | 0.030     | 0.037 | 0.55        | 0.75    | 0.95  |  |  |

| ORDERING INFORMATION                          |                                             |  |  |  |  |  |

|-----------------------------------------------|---------------------------------------------|--|--|--|--|--|

| Part Number                                   | Number     Package Type     Production Flow |  |  |  |  |  |

| SG500DYB 28 PIN SSOP Commercial, 0°C to +70°C |                                             |  |  |  |  |  |

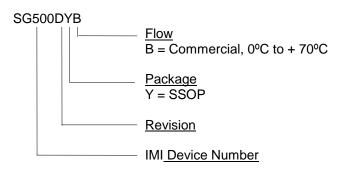

<u>Note</u>: The ordering part number is formed by a combination of device number, device revision, package style, and screening as shown below.

Marking: Example: IMI SG500DYB Date Code, Lot #